随着半导体制程工艺的升级难度越来越大,进度越来越缓慢,台积电的7nm工艺开发成本已经超过了30亿美元,接下来的5nm工艺预计要超过50亿美元,在平面上想提升晶体管密度这事情已经变得相当有挑战性,3D度堆叠工艺可能是解决这问题的一个好方法,结构简单的NAND闪存已经大面积转向3D堆叠工艺了,HBM显存也是利用3D堆叠工艺生产的,但是3D堆叠工艺也不是万能的,散热就是3D堆叠工艺要面临的一大难题,层数越多热量堆积就越严重,AMD近日申请的一项专利就有可能解决这一问题的。

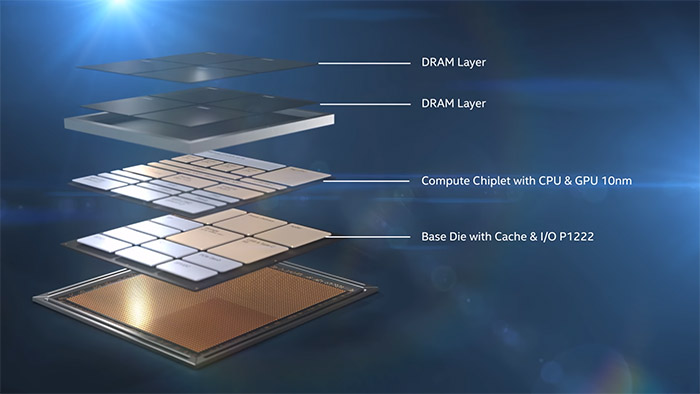

CPU也要上3D堆叠工艺了,这是Intel采用Foveros 3D封装工艺所生产的Lakefield SoC

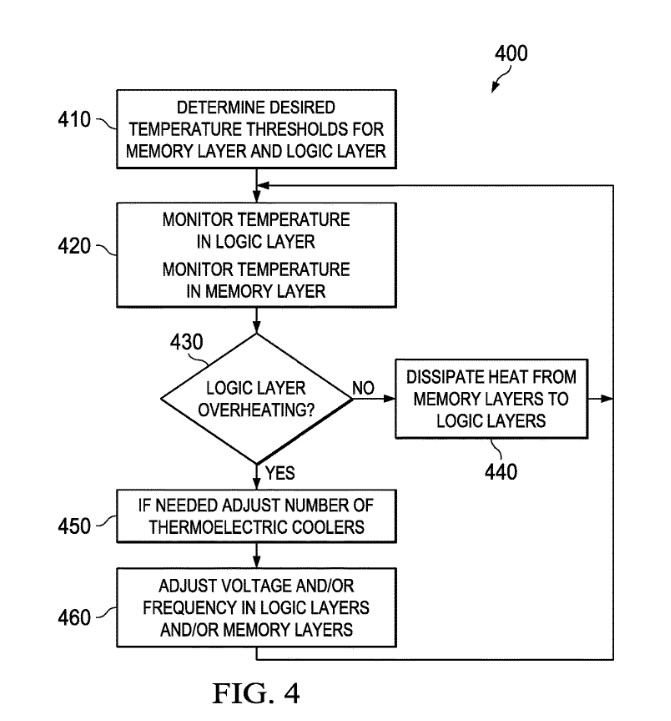

AMD这一专利的就是在3D堆叠内存的逻辑层和存储层之间插入一片TEC热点效应散热模组,也就是我们所说的半导体制冷器或温差制冷器,它利用珀尔帖效应,由N、P型材料组成一对热电偶,当热电偶通入直流电流后,因直流电通入的方向不同,将在电偶结点处产生吸热和放热现象。

而这个现象是可以根据电流的方向而反转的,也就是说可以根据传感器反馈的结果,都可以利用热电偶把热量从较高的那一端转移到温度较低的一端,让热量分布更为平均,这一专利在任何3D堆叠生产的芯片上都相当实用,然而这一过程是会产生额外的发热的,也会带来额外的功耗,所以这一专利是否真的有用我们还得等实际产品出来再说。

超能网友研究生 2019-07-01 11:32 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(38) | 反对(0) | 举报 | 回复

3#

超能网友研究生 2019-07-01 22:00 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有2次举报支持(1) | 反对(1) | 举报 | 回复

8#

超能网友教授 2019-07-01 21:53 | 加入黑名单

支持(3) | 反对(0) | 举报 | 回复

7#

我匿名了 2019-07-01 16:26

支持(1) | 反对(0) | 举报 | 回复

6#

超能网友研究生 2019-07-01 14:38 | 加入黑名单

支持(17) | 反对(0) | 举报 | 回复

5#

超能网友终极杀人王 2019-07-01 13:34 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有13次举报支持(0) | 反对(13) | 举报 | 回复

4#

超能网友教授 2019-07-01 10:16 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(5) | 反对(0) | 举报 | 回复

2#

游客 2019-07-01 10:15

该评论年代久远,荒废失修,暂不可见。

支持(1) | 反对(0) | 举报 | 回复

1#