欢迎参与评论,每一条合规评论都是对我们的褒奖。

请 登录 或 快速注册 后发表评论

西部数据和恺侠(原东芝存储)在1月30日宣布他们的第五代3D堆叠NAND闪存BiCS 5,将会用于TLC和QLC的生产,堆叠层数是112层,当我看到这层数时就觉得事情好像有点不对了,去年不是说BiCS 5有128层的吗?

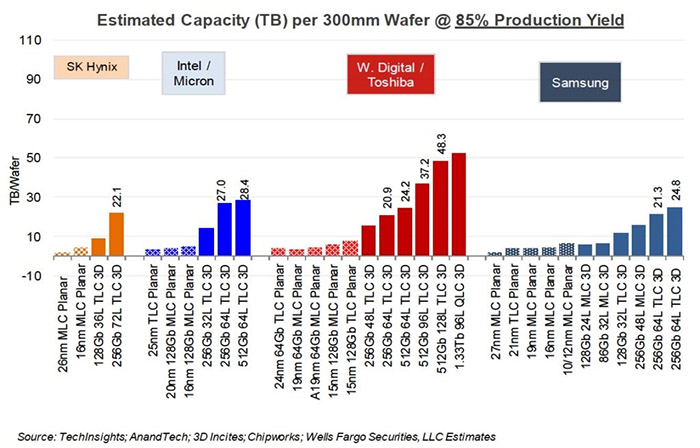

其实在去年的ISSCC会议上东芝和西数就公布过他们的128层堆叠BiCS 5闪存的部分资料了,就存储密度而言东芝和西数的128层堆叠512Gb 128层3D TLC确实很高,不过更高端是他们的1.33Tb的96层堆叠3D QLC,不过现在公布出来的BiCS 5数据和当时的相比有所缩水,现在恺侠方面则是称BiCS 5存储单元阵列的密度相对于上一代技术有20%的提升,而当时宣布的是128层堆叠3D TLC和96层的3D TLC比起来存储密度提升了29.8%。

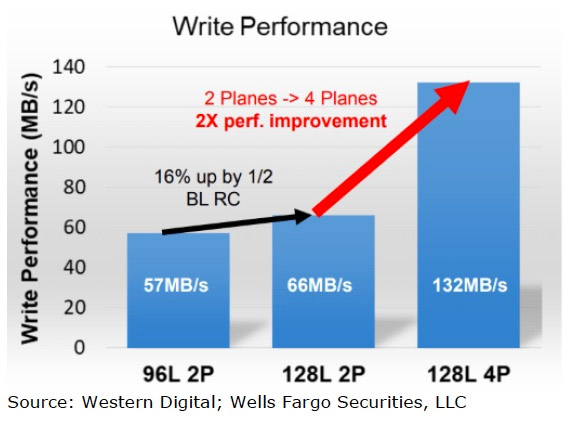

性能方面其实也有缩水的,去年公布时128层的闪存会采用单die采用4 Planes设计,而与2 Planes设计相比写入速度从66MB/s提升到132MB/s,而96层的2 Planes写入速度只有57MB/s,可见写入速度是番了一倍多的,而现在发布的BiCS 5只说在I/O性能上会比BiCS4高出50%。

当然我不是说现在的BiCS 5不好,因为它和BiCS 4相比在堆叠层数、性能、存储密度上都有明显提升,只不过没有当初预想值那么好而已,可能128层的在生产上遇到了问题,所以折中拿了现在的112层的出来,他们应该权衡过认为先量产还等更好的产品出来这个问题,说真的与其死等好的产品与工艺成熟,还不如先拿这种比较折中的方案出来抢市场实际些。