台积电(TSMC)董事长刘德音(Mark Liu)博士在2021年国际固态电路会议(ISSCC)以《揭秘创新未来》为主题做了线上专题演讲,证实了台积电下一代3nm工艺节点正按计划有序推进,目前正在建设生产3nm芯片的设施,希望明年开始可以按计划进行批量生产。

Wccftech认为有个别媒体误解了演讲内容,认为3nm工艺节点的研发已提前完成,事实上整个演讲里面对开发时间表提及的篇幅不多。

刘博士除了提到台积电研发的一些情况外,也谈及了对工艺发展的看法,另外还强调了到目前为止,台积电已经出货了大约18亿颗采用7nm工艺节点制造的芯片。

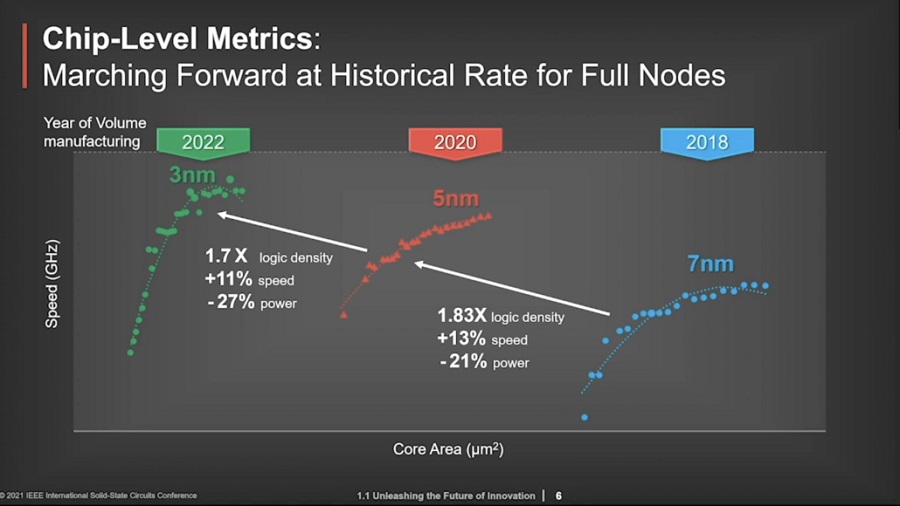

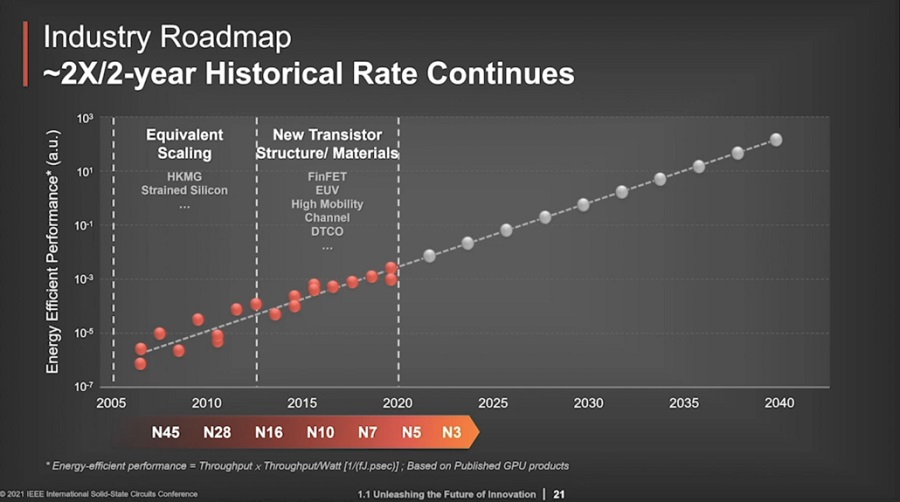

技术方面包括EUV光刻机的使用、新的晶体管技术、新材料的应用、芯片小型化以及新的封装技术等一系列通向未来的突破性半导体技术。在各种技术加持下,工艺节点路线图能保持每两年大约2倍的能效性能提升。台积电5nm工艺节点正是顺应了这一趋势,接下来的3nm工艺节点也会如此。

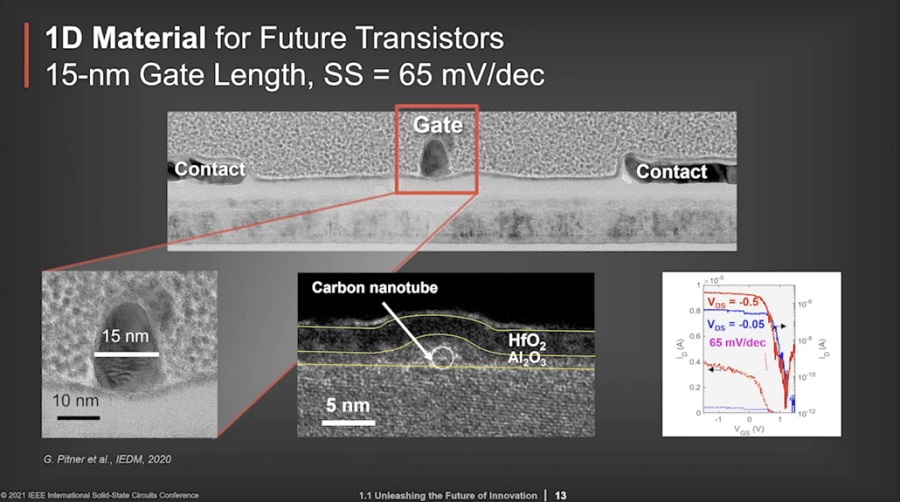

刘博士介绍了台积电未来的一些研发计划,例如碳纳米管,不过使用碳纳米管的晶体管通道的一个关键问题是需要开发一种栅极介电材料,使晶体管的栅极长度较短。现在已经可以做到这一点,适合于10nm栅极长度的晶体管。

还有开发低维材料,比如六方氮化硼,可以在较低的制造温度下转移到任意晶圆衬底上,为在三维中制造逻辑芯片和存储器层开辟了道路。

台积电在5nm工艺节点引入一种名为high mobility channel(HMC)的晶体管,将锗材料整合到了晶体管中,导线中也利用了钴与钌材料。在3nm工艺节点之后会采用gate-all-around(GAA)晶体管,采用nanosheet结构。

刘博士强调在过去几年中,台积电采用了设计-技术协同优化(Design Technology Co-Optimization,DTCO),对芯片制造来说变得越来越重要。因为允许他们同时使用设计和制造技术来跟上性能要求,这使得台积电在衡量一个工艺节点逻辑密度的时候,已经超越原来诸如栅极间距等指标,使得3nm比5nm工艺节点的逻辑密度提高了1.8倍。

半导体制造工艺已成为全球的焦点,因为社会生产和生活中对硅的需求不断增长,对相关企业的需求也创下了新纪录。由于供不应求,导致各行各业都面临芯片短缺的问题,目前已经导致汽车厂商的生产中断。

超能网友高中生 2021-02-26 15:41 | 加入黑名单

支持(1) | 反对(0) | 举报 | 回复

7#

超能网友教授 2021-02-25 11:11 | 加入黑名单

支持(0) | 反对(0) | 举报 | 回复

6#

超能网友教授 2021-02-25 09:47 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(1) | 反对(0) | 举报 | 回复

5#

超能网友一代宗师 2021-02-25 08:09 | 加入黑名单

支持(2) | 反对(0) | 举报 | 回复

4#

超能网友终极杀人王 2021-02-24 20:53 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有4次举报支持(0) | 反对(4) | 举报 | 回复

3#

超能网友大学生 2021-02-24 15:54 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(4) | 反对(1) | 举报 | 回复

2#

超能网友教授 2021-02-24 15:26 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有6次举报支持(6) | 反对(10) | 举报 | 回复

1#