在今天凌晨的New Horizon会议上,AMD正式宣布了全球第一个7nm数据中心服务器以及7nm数据中心显卡,会议内容很多,先来看看CPU方面的。这次宣布的是代号Rome罗马的新一代EPYC服务器处理器,使用了台积电7nm工艺以及Zen 2架构,从之前最多32核64线程提升到了64核128线程,同时支持PCIe 4.0,目前新一代EPYC已经出样,并获得亚马逊等厂商的认可,后续的Zen 3架构已经在路上,Zen 4架构则在开发中。

首先来看官方PPT中对Zen 2架构及7nm工艺的具体介绍:

AMD路线图中,Zen及Zen+架构分别使用14nm、12nm工艺,已经上市了,7nm Zen 2架构处理器已经出样,Zen 3架构将使用7nm+工艺,也就是7nm EUV工艺,目前进展正常,按部就班进行中。

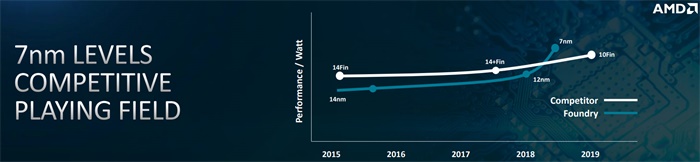

7nm工艺的优点

对外界来说,7nm工艺是AMD近年来首次在制程工艺上领先英特尔处理器,对AMD自己来说,7nm工艺带来的好处主要是技术方面的,晶体管密度提升一倍,功耗降低50%,同功耗下性能提升25%——在隔壁的7nm Vega上,AMD提到的数据是降低50%能耗,性能提升30%。

与竞争对手的工艺对比

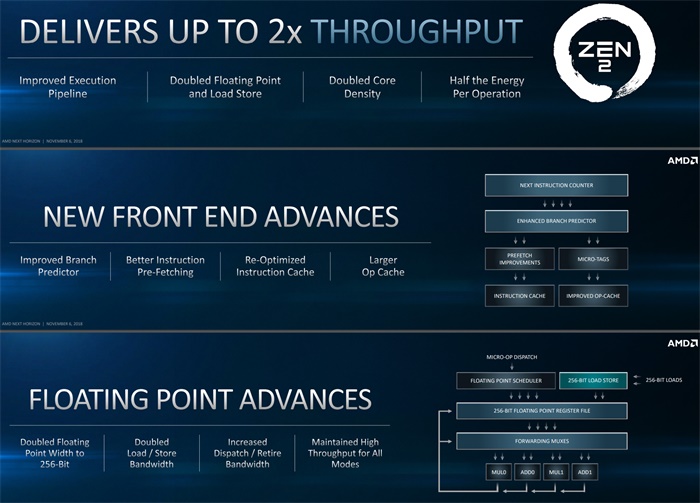

Zen 2架构改进一览

除了7nm工艺,代号罗马的EPYC处理器也升级到了Zen 2架构,AMD表示它在执行单元、安全性以及模块化设计、生产性方面也做了改进。

Zen 2架构核心改进

Zen 2架构在前端、浮点、缓存等方面都做了改进,改善了执行单元,加倍了浮点位宽到256bit、加倍了核心密度、降低了一半的操作功耗等等。

安全性增强

罗马处理器主打数据中心市场,安全性也非常重要,Zen 2架构在内存加密、软件以及幽灵漏洞方面都做了加强。

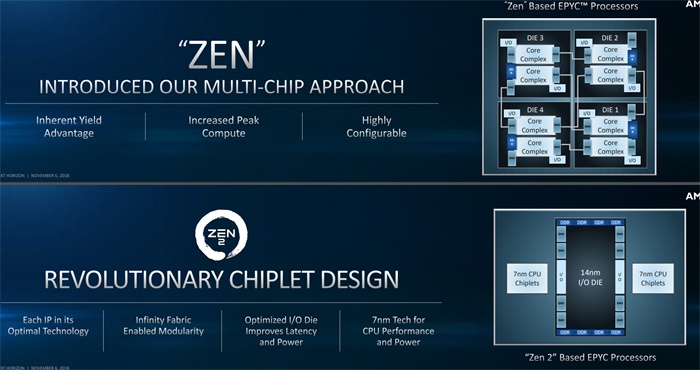

Zen 2架构的多芯片封装

Zen 2架构另一个变化就是多芯片封装了,从首图可以看到Zen 2内部的模块跟Zen一代的不同了,因为AMD在Zen 2设计的是I/O核心外置+CPU核心的结构,而且使用的是不同的工艺,简单来说就是Zen 2处理器中有一个14nm工艺的I/O核心(包括DDR内存控制器),周围排布的则是7nm Zen 2核心。

对于这种设计,AMD表示它的优点很多,可以提高良率,具备更高的可配置性,或许这就是Zen 2处理器能够实现64核128线程的关键了,毕竟按照传统思路做下去,64+核心带来的难度及良率考验都是超常规的。

对于这种架构,最大的担心还是内存延迟之类的,不过现在提这个还太早,这个问题等有了详细资料再来讨论。

Zen 2架构总结

AMD Zen架构处理器路线图

游客 2018-11-07 20:21

该评论年代久远,荒废失修,暂不可见。

支持(110) | 反对(2) | 举报 | 回复

32#

超能网友终极杀人王 2018-11-07 11:26 | 加入黑名单

本评论因举报过多被折叠 [+]14#

游客 2019-05-29 10:41

已有1次举报支持(0) | 反对(2) | 举报 | 回复

66#

游客 2019-04-16 07:17

支持(4) | 反对(0) | 举报 | 回复

65#

游客 2019-03-20 12:33

支持(0) | 反对(0) | 举报 | 回复

64#

游客 2018-11-15 19:46

已有3次举报支持(5) | 反对(0) | 举报 | 回复

63#

超能网友终极杀人王 2018-11-13 23:54 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

62#

游客 2018-11-09 08:57

该评论年代久远,荒废失修,暂不可见。

已有2次举报支持(1) | 反对(0) | 举报 | 回复

61#

游客 2018-11-08 19:58

该评论年代久远,荒废失修,暂不可见。

已有3次举报支持(2) | 反对(2) | 举报 | 回复

60#

游客 2018-11-08 19:39

已有3次举报支持(6) | 反对(1) | 举报 | 回复

59#

游客 2018-11-08 18:20

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(1) | 举报 | 回复

58#

我匿名了 2018-11-08 18:04

已有8次举报支持(1) | 反对(1) | 举报 | 回复

57#

游客 2018-11-08 17:26

已有7次举报支持(1) | 反对(1) | 举报 | 回复

56#

超能网友博士 2018-11-08 16:07 | 加入黑名单

已有2次举报支持(0) | 反对(1) | 举报 | 回复

55#

游客 2018-11-08 12:17

本评论因举报过多被折叠 [+]54#

游客 2018-11-08 10:35

该评论年代久远,荒废失修,暂不可见。

已有4次举报支持(2) | 反对(0) | 举报 | 回复

53#

游客 2018-11-08 09:44

该评论年代久远,荒废失修,暂不可见。

已有2次举报支持(3) | 反对(0) | 举报 | 回复

52#

游客 2018-11-08 09:30

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(2) | 反对(0) | 举报 | 回复

51#

游客 2018-11-08 09:03

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(4) | 反对(0) | 举报 | 回复

50#

游客 2018-11-08 08:49

已有1次举报支持(1) | 反对(0) | 举报 | 回复

49#

游客 2018-11-08 08:35

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(2) | 反对(0) | 举报 | 回复

48#

游客 2018-11-08 04:47

该评论年代久远,荒废失修,暂不可见。

支持(3) | 反对(0) | 举报 | 回复

47#

超能网友一代宗师 2018-11-08 04:32 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(7) | 反对(0) | 举报 | 回复

46#

游客 2018-11-08 02:23

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(12) | 反对(1) | 举报 | 回复

45#

游客 2018-11-08 01:32

该评论年代久远,荒废失修,暂不可见。

已有6次举报支持(0) | 反对(4) | 举报 | 回复

44#

游客 2018-11-08 01:08

已有1次举报支持(17) | 反对(0) | 举报 | 回复

43#

游客 2018-11-08 01:00

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(16) | 反对(0) | 举报 | 回复

42#

超能网友终极杀人王 2018-11-07 23:15 | 加入黑名单

支持(8) | 反对(0) | 举报 | 回复

41#

游客 2018-11-07 22:46

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(13) | 反对(0) | 举报 | 回复

40#

我匿名了 2018-11-07 22:36

该评论年代久远,荒废失修,暂不可见。

支持(8) | 反对(0) | 举报 | 回复

39#

加载更多评论