Haswell芯光大道系列文章参阅:

《Haswell芯光大道之一,支持C7节能的电源推荐》

《Haswell芯光大道之二,FIVR集成式调压模块详解》

对于Haswell处理器,Intel在多个重要场合已经强调了它的重要之处,留给大家印象最深的恐怕是官方展示的GPU性能,GT3e都可以跟NVIDIA主流的GT 650M相提并论了。在核显之外,Haswell最引人注目的地方就在于各种节能设计了。

今天这篇文章就来讲讲Haswell节能设计的一个重大基础——调压模块VRM(Voltage Regulator Module,也有只叫VR的)的变化,它的加入使得Haswell在功耗管理与控制上如虎添翼。

FIVR集成式调压模块:一片顶五片

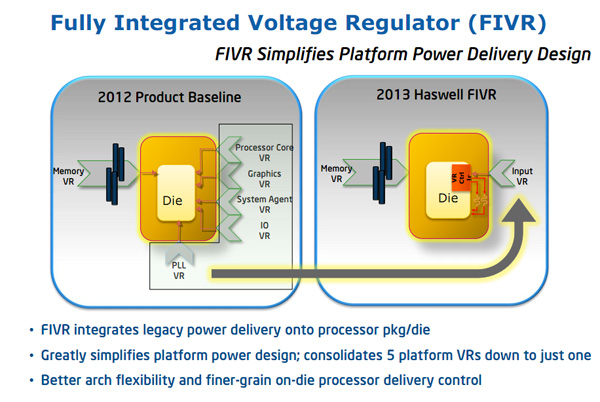

Haswell之前的处理器与Haswell处理器的VR模块的变化

在Haswell之前,整个处理器的VR模块可以分为Core VR、Graphics VR、PLL VR、System Agent VR及IO VR,这五个VR模块再加上Memory内存VR都是位于主板上的,Haswell将前面5个VR模块整合成一个,并且集成到了CPU内部,主板上只留下Memory VR模块。

这个集成式的VR模块叫做FIVR(全集成式电压调节模块),之前也叫ISVR(Integrated Silicon Voltage Regulator),还有简单叫IVR的,反正都是这一个东西。Intel研究这个FIVR已经有几年的时间了,无所不能的IBM也研究过这个东西,只不过IBM兴趣早就不在这些小东西上了,Intel最终在Haswell这一代处理器上集成了FIVR设计。

FIVR的实现:2.8mm2专用电路单元,最多320相

FIVR有专用的Power Cell电路

FIVR把主板上的功能集成到了CPU内,这就需要CPU芯片单独划出一部分电路来控制。Haswell中,每个CPU内都有单独的Power Cell电路,内有16相PWM电路,核心面积2.8平方毫米,每个处理器内最多可有20个Power Cell单元,最多320相供电,核心面积也会增加,按照20个cell来算这就是56平方毫米了,相对核心面积只有100平方毫米的CPU来说不小了。

当然,Intel官方公布的资料里也没具体说明Haswell处理器到底集成了多少个Power Cell单元,实际上不会有20个这么多,从之前公布的测试来看,我觉得5个都算多了。

Power Cell架构:每路电流25A,开关频率最高140MHz

据Intel所说,每个Power Cell单元实际上就相当于一个最小的VR电路(上桥MOSFET+驱动电路),支持通过电流25A(每相电路相当于1.56A),20个Cell电路就相当于500A电流,远远高于CPU正常所需的电流。此外,其开关频率可达30-140MHz,这样单纯的数据没有什么意义,我们以技嘉主板的超耐久5用料中的IR3550 MOSFET,其开关频率为1MHz,就算把最顶级的MOSFET算上,Haswell的Power Cell电路的开关速度都是它的30-100倍以上,而开关频率越高,电流输出就会越平稳。

最后,Power Cell中的每相电路的自身电感值只有17nH(纳亨),而主板上使用的电感大都是R56或者R80的,电感值为0.56/0.80 uH(微亨),相当于560/800 nH。

需要注意的是,我们现在看到的这些FIVR模块数据实际上都是基于90nm工艺制造的,也就是说如果Intel打算用更先进的制程工艺来生产Power Cell电路,那么其核心面积还会进一步减小,性能也可以更高。

FIVR模块的意义:更精确的供电控制,更高的能效

Intel不惜以增加核心面积和功耗的代价在Haswell处理器上使用FIVR模块,这说明FIVR带来效果肯定是利远大于弊。通过FIVR,Haswell处理器的每个内核的的供电管理会更佳精细化,直接好处就是电压波纹更低,能效更高。

集成电压模块的波纹只2mV左右

按照Intel的测试,FIVR的电压波纹只有2mV左右,目前高端主板的波纹能做到10-20mV,一般的主板能做到50-80mV就不错了,2mV的波纹绝对是惊人的水平。

能效更高

传统的设计中峰值最高效率也只有76%,FIVR可以轻松达到82%的水平。

对厂商来说,供电设计也可以简化

Intel还对比了与主板上的VR模块的体积问题,FIVR具备400A以上供电能力,传统主板设计普遍是120A左右(实际上高端主板普遍是12相,每相电路一般认为30A供电能力,差不多也有400A的供电能力),而且FIVR的最大特色就是体积更小,二者完全不在一个量级上。

总结:主板供电大大简化,FIVR代表未来

初看Intel的FIVR设计还以为它能取代主板上的PWM电路呢,实际上FIVR目前还不具备这个功能,因为它只是个高精度高精细化的调节模块,还需要主板的PWM电路提供基本电压调节。另外,Memory VR模块还是独立在主板上的。

但是FIVR的出现对主板供电电路要求大大降低,主板只需要提供基本的供电输出就OK,以前动辙几十相供电的主板在8系列主板中基本上不会多见(不排除还有少数纯堆料的主板),再多相的主板供电其纹波也不可能达到2mV吧,高精度调节的工作就交给FIVR去做。

另一方面就是FIVR的精细化调节,让系统更加省电。它能独立调节每个内核、显卡核心、SA系统助手以及内部的I/O总线等各个部分供电,不需要的部分就关闭掉。比如播放视频,基本只要GPU解码参与就行,FIVR通过精细化调节让Ring-Bus总线全速运行,同时关闭CPU供电,这样功耗会降低许多。

FIVR代表的是未来,更精确精细化的供电控制可以让Intel更好地调控CPU核心或者整个处理器的功耗与发热,可以实现哪里不用关哪里的效果,带来更深层的C节能状态。

有一种观点认为FIVR集成到CPU内会增加处理器的功耗和发热,比如Haswell桌面版的TDP从77W增加到84W、移动版从最高55W增加到57W就是一个证据,但是个人认为这种说法还有可商榷之处,Power Cell在90nm工艺下面积也只有2.8mm2,如果Haswell上这部分电路也是22nm 3D晶体管工艺,那么核心面积和发热会非常低,而TDP升高有可能是GT3/GT2核显带来的。

每个内核都可以独立控制

目前的CPU内核电压虽然是可以变化的,但是每个内核电压都是一样的,而FIVR及更先进的VR技术未来可以单独控制每个内核的电压,根据需要分配最优电压,这就跟Silvermont架构上首次实现X86架构中的异步频率运行差不多,而高通早就在旗下的移动处理器中实现了不同电压不同频率的异步运行模式,或许未来我们就能看到Intel的处理器具备类似的功能了。

游客 2013-08-19 07:46

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

13#

游客 2013-08-19 07:44

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

12#

游客 2013-05-17 15:12

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

11#

游客 2013-05-15 16:34

该评论年代久远,荒废失修,暂不可见。

支持(3) | 反对(0) | 举报 | 回复

10#

我匿名了 2013-05-14 10:32

该评论年代久远,荒废失修,暂不可见。

支持(2) | 反对(0) | 举报 | 回复

9#

游客 2013-05-13 22:20

该评论年代久远,荒废失修,暂不可见。

支持(7) | 反对(0) | 举报 | 回复

8#

游客 2013-05-13 17:22

该评论年代久远,荒废失修,暂不可见。

支持(1) | 反对(0) | 举报 | 回复

7#

游客 2013-05-13 15:58

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(1) | 举报 | 回复

6#

游客 2013-05-13 14:31

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

5#

超能网友管理员 2013-05-13 14:00 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(1) | 反对(0) | 举报 | 回复

4#

游客 2013-05-13 12:42

该评论年代久远,荒废失修,暂不可见。

支持(1) | 反对(0) | 举报 | 回复

3#

超能网友终极杀人王 2013-05-13 12:26 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(0) | 反对(0) | 举报 | 回复

2#

我匿名了 2013-05-13 12:04

该评论年代久远,荒废失修,暂不可见。

支持(2) | 反对(0) | 举报 | 回复

1#