早在2017年Intel推出HEDT平台的Skylake-X架构处理器时,他们就尝试对处理器缓存架构进行修改,把L3缓存从每核心2.5MB变成了每核心1.375MB,缩减的部分被用来扩大L2缓存了,从以前的256KB提升到1MB,这样做可以提升L2的命中率降低访问延迟,提升IPC,但这些改动并没有应用到大众平台上,从Skylake到Coffee Lake,架构就一直没改过,一直到10nm的Ice Lake缓存才有所改动。

而现在Geekbench数据库上有了下一代10nm处理器Tiger Lake的资料,看来Intel打算进一步对缓存架构进行修改,这款四核八线程的Tiger Lake-Y的L1缓存和现在的Ice Lake是一样的,每核心有48KB L1数据缓存和32KB L1指令缓存,但Tiger Lake的每核心L2缓存增加到1.25MB,而现在的Ice Lake处理器只有512KB,Skylake更是只有256KB,很明显L2缓存被Intel大幅增加了,而且L3缓存也没有像Skylake-X那时相对缩小了,反而还增加了50%,现在核心的Tiger Lake就有12MB L3缓存,而同样核心数量的Skylake和Ice Lake都只有8MB L3。

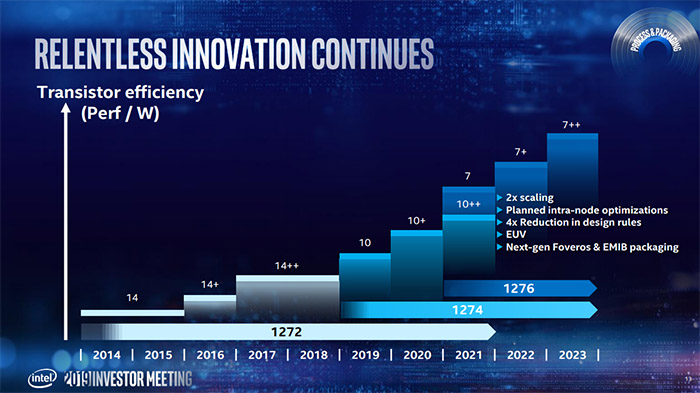

Tiger Lake可能还会加入对PCI-E 4.0的支持,并且会拥有多达96EU的Xe核显,预计Tiger Lake会在2020年到2021年的某个时间投入到市场上,但是Intel现在的10nm产能还是很堪忧的,不然他们也不会一直没法彻底转向Ice Lake,现在绝大部分产品依然是采用14nm++工艺的,而Tiger Lake用的已经是第三代的10nm++工艺了(Ice Lake算第二代,第一代是Cannon Lake),所以大家慢慢等吧。

游客 2019-12-03 01:58

该评论年代久远,荒废失修,暂不可见。

支持(4) | 反对(0) | 举报 | 回复

6#

超能网友终极杀人王 2019-12-02 13:52 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

已有1次举报支持(14) | 反对(1) | 举报 | 回复

5#

超能网友一代宗师 2019-12-02 13:01 | 加入黑名单

该评论年代久远,荒废失修,暂不可见。

支持(3) | 反对(0) | 举报 | 回复

4#

我匿名了 2019-12-02 12:53

该评论年代久远,荒废失修,暂不可见。

支持(7) | 反对(0) | 举报 | 回复

3#

我匿名了 2019-12-02 11:43

该评论年代久远,荒废失修,暂不可见。

支持(14) | 反对(1) | 举报 | 回复

2#

游客 2019-12-02 10:46

该评论年代久远,荒废失修,暂不可见。

支持(14) | 反对(1) | 举报 | 回复

1#