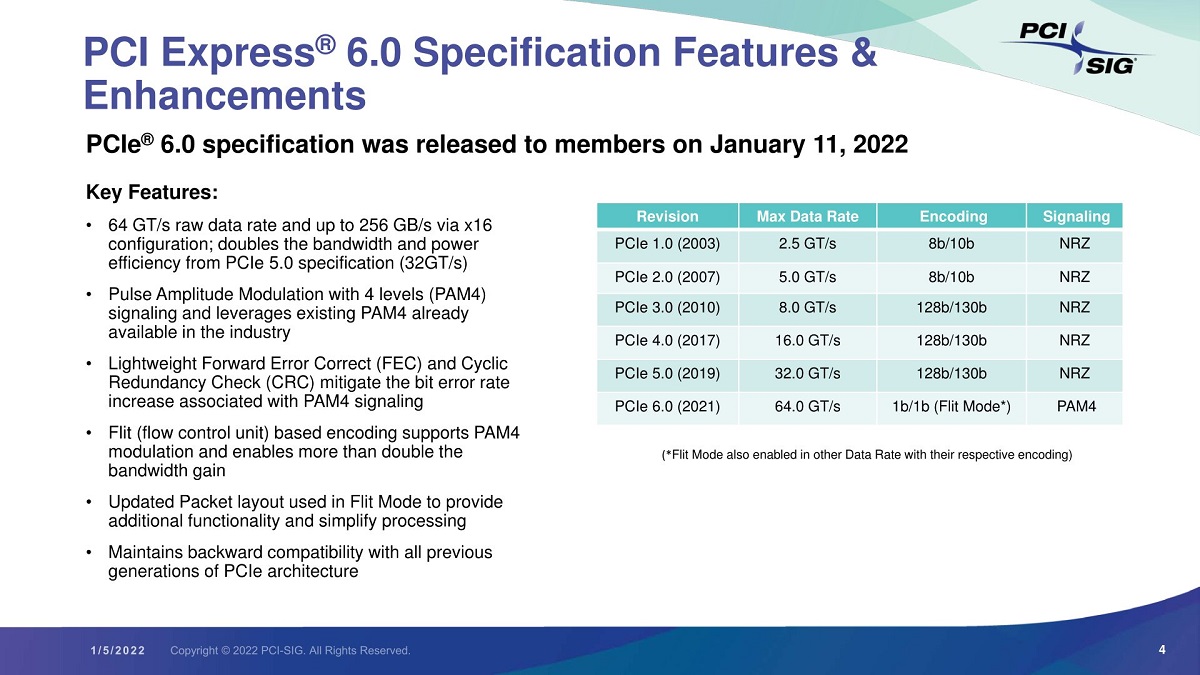

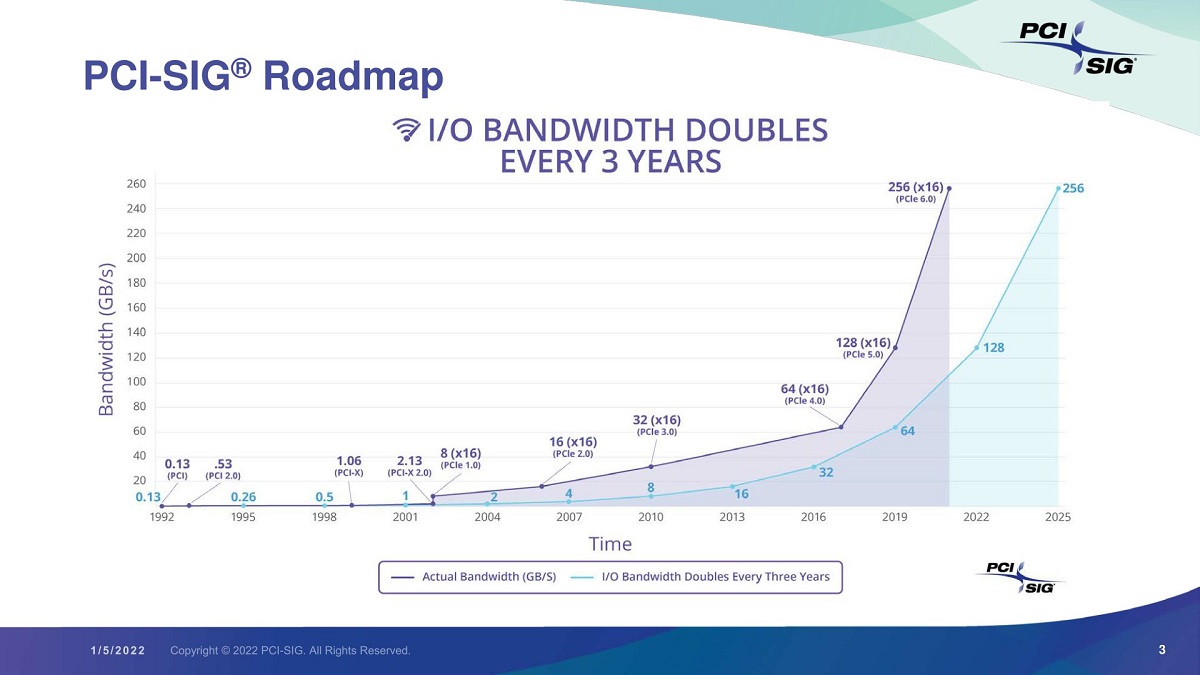

PCI-SIG在2019年6月开始PCIe 6.0规范的相关制定工作,在经历了两年零七个月后,PCI-SIG在2022年1月正式向其成员发布PCIe 6.0规范。新规范是在PCIe 5.0规范发布不到三年后推出的,同时也兑现了PCI-SIG的承诺,即每发布一个PCIe新规范就会让带宽翻倍。

PCIe 6.0规范的发布,将有利于数据密集型市场,比如高性能计算(HPC)、数据中心、边缘计算、人工智能和机器学习(AI/ML)、汽车、物联网(IoT)以及航空航天等,并进一步加强了PCI Express作为高速互联的接口。

PCIe 6.0规范的主要优势在于:

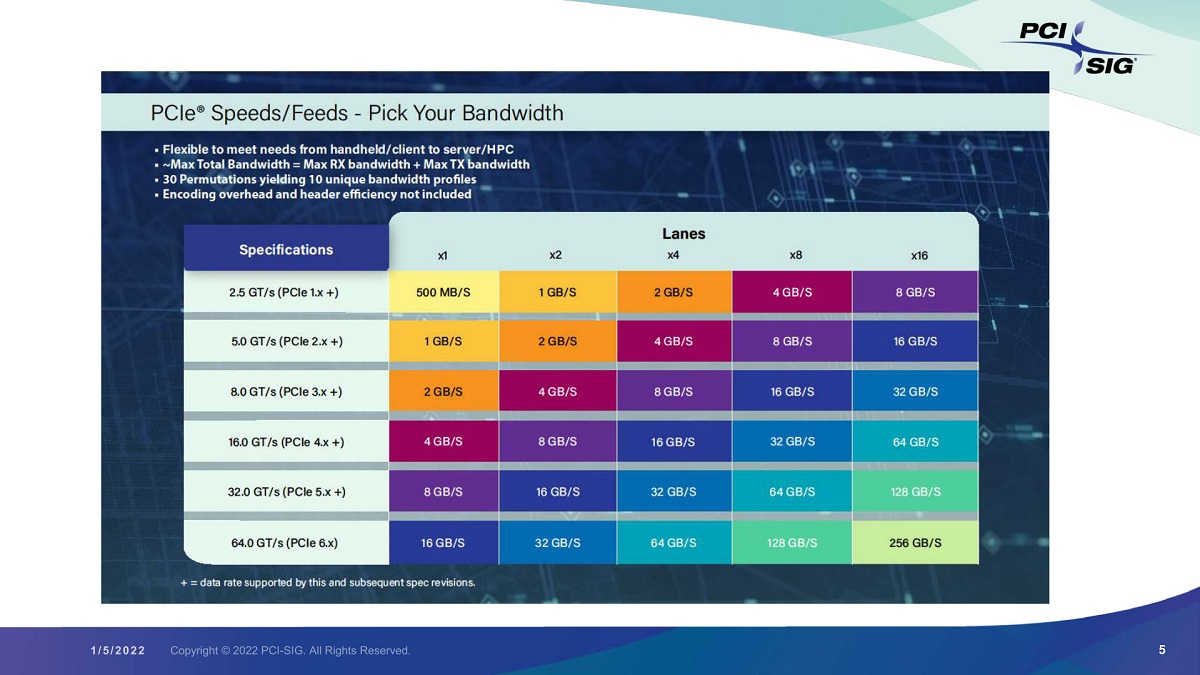

带宽加倍:将数据传输速率提高到64 GT/s,相比PCIe 5.0规范提高了一倍,16通道可以提供高达256 GB/s的最大双向带宽。

低延迟: 利用基于固定大小流控制单元(Flit)的编码,允许使用低延迟前向纠错(FEC)和四级脉冲幅度调制(PAM4)信令和强循环冗余校验(CRC)。

向后兼容性: 保持与以往PCIe技术的兼容性,支持与数以万计现有产品的连接。

就像PCI-SIG设计的其他规范一样,每个PCI Express规范都会有五个主要的节点。

0.3版本:概念。该草案描述了需要实现的目标和实现这些目标的方法。就PCIe 6.0而言,是指提出了64 GT/s数据传输速率、PAM4信令和FEC。

0.5版本:第一稿。这个版本必须完全解决0.3草案中设定的目标,它还包括所有的架构方面和要求。此外,它还包含了来自各相关方的反馈意见,此时PCI-SIG的成员可以将功能添加到正在制定的规范中。PCI-SIG在2020年2月底发布了PCIe 6.0规范的0.5版本。

0.7版本:完整草案。这个版本必须有一套完整的功能需求和方法定义,因为在这个版本之后不能再增加新的功能了。此外,电气规范必须已经使用测试芯片进行了验证。在这一点上,PCI-SIG成员可以提出新接口的不同实现。

0.9版本:最终草案。此时,PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。同时,不允许进行任何功能上的修改。

1.0版本:最终版本。从这个版本开始,所有的更改和增强都必须通过正式的勘误表文档和工程变更通知(ECN)。

相关支持PCIe 6.0规范的产品,很可能要到2023年底或2024年的某个时候才会上市。这个可以参考此前的PCIe 5.0规范,PCI-SIG是在2019年5月底公布了PCIe 5.0规范的最终版本,实际上首批支持该技术的产品直到2021年底才出现。

wqxhrl博士 2022-01-13 09:14 | 加入黑名单

以后显卡跑PCIE6.0 x8就够了,剩下的可以干其他事了。

支持(0) | 反对(0) | 举报 | 回复

5#

xaaaaaaaaaaaaaa一代宗师 2022-01-12 17:26 | 加入黑名单

PAM4真的可以吗?会不会功耗炸裂?

支持(4) | 反对(0) | 举报 | 回复

4#

我匿名了 2022-01-12 16:28

支持(4) | 反对(0) | 举报 | 回复

3#

vigo93终极杀人王 2022-01-12 15:51 | 加入黑名单

intel:懂了 十三代上pcie6.0 超大提升 要换新主板噢

已有5次举报支持(2) | 反对(4) | 举报 | 回复

2#

itck终极杀人王 2022-01-12 12:13 | 加入黑名单

这个插座和pcb需要什么形态才能稳定跑的出这种带宽…………

支持(4) | 反对(0) | 举报 | 回复

1#

提示:本页有 5 个评论因未通过审核而被隐藏