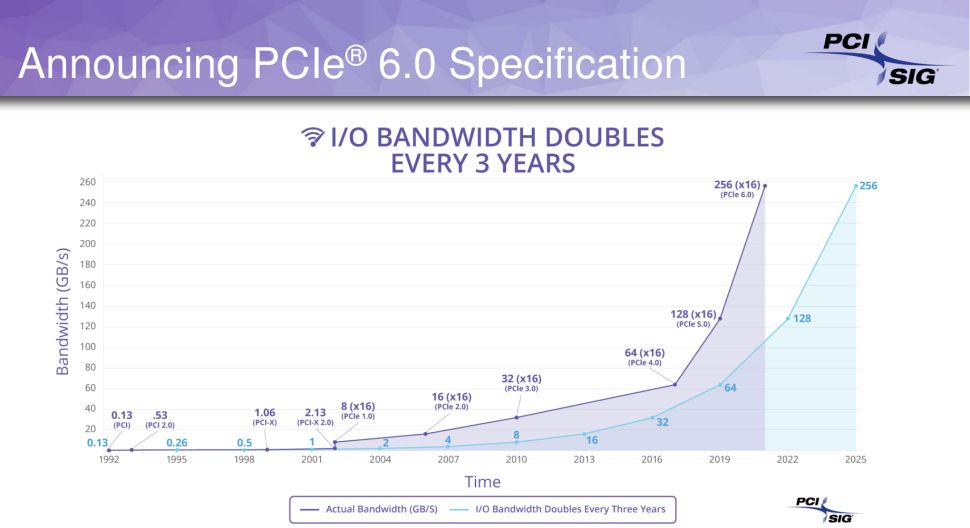

PCI-SIG在过去近30年的时间里,不断推出新的I/O标准,满足新一代系统所需带宽的增长。此外,尽可能保留对上一代接口的兼容性,以保证设备的适用范围。从最早的133 MB/s到最新的64 GB/s(PCIe 5.0 x16单向理论数据传输速度),已增长了480倍。

近日,英特尔发布了第12代酷睿系列处理器(Alder Lake),新平台首次支持PCIe 5.0,让普通消费者有了与PCIe 5.0接触的机会。

PCIe 5.0也称为PCI Express 5.0,准确来说叫第5代快速周边组件互连。自2003年首次提出PCIe技术后,早已成为使用点对点访问总线将高速组件连接到主板的标准接口,取代了以往主板上的ISA、PCI、AGP、AMR和CNR等接口。

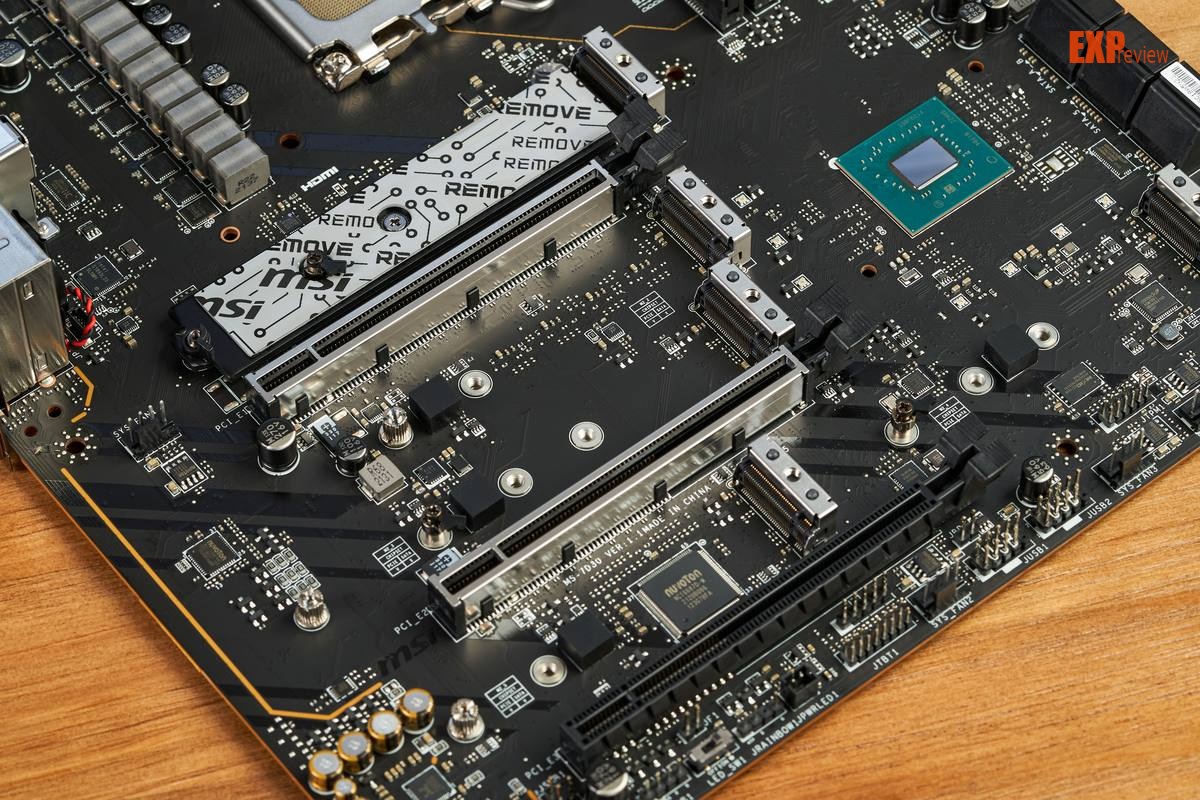

图:微星MPG Z690 CARBON WIFI主板的PCIe 5.0 x16插槽

就像PCI-SIG设计的其他规范一样,每个PCI Express规范都有五个主要的节点。

0.3版本:概念。该草案描述了需要实现的目标和实现这些目标的方法。

0.5版本:第一稿。这个版本必须完全解决0.3草案中设定的目标,它还包括所有的架构方面和要求。此外,它还包含了来自各相关方的反馈意见,此时PCI-SIG的成员可以将功能添加到正在制定的规范中。

0.7版本:完整草案。这个版本必须有一套完整的功能需求和方法定义,因为在这个版本之后不能再增加新的功能了。此外,电气规范必须已经使用测试芯片进行了验证。在这一点上,PCI-SIG成员可以提出新接口的不同实现。

0.9版本:最终草案。此时,PCI-SIG成员正在对技术进行内部审查,以确保其知识产权和专利。同时,不允许进行任何功能上的修改。

1.0版本:最终版本。从这个版本开始,所有的更改和增强都必须通过正式的勘误表文档和工程变更通知(ECN)。

PCI-SIG早在2019年5月底公布了PCIe 5.0规范的1.0版本,不过首批支持该技术的产品直到现在才出现。

PCIe 5.0向后兼容PCIe 4.0及之前的规范,通过改变电气设计改善信号完整性和机械性能,新标准减少了延迟,降低了长距离传输的信号衰减。与之前的PCIe 4.0相比,PCIe 5.0依然采用同样的128b/130b编码方式、目标比特误码率(BER)、信令和加扰方案等,但更改了EIEOS和数据比特率定义等。此外,还有其他的设计更改,比如二阶响应的时钟数据恢复(CDR)和CEM连接器。

PCIe 5.0带来了更高传输速度,x16带宽(双向)从PCIe 4.0的64 GB/s提升到了128 GB/s,提高了设备传输速率的上限,以满足数据中心、高性能计算、边缘计算、机器学习、人工智能和5G网络等场景里日益增长的带宽需求,也可以让设备制造商用更少的通道数实现同样的带宽。相比从PCIe 3.0到PCIe 4.0所用的时间,PCIe 4.0到PCIe 5.0的过渡显然要快得多。

在2019年,英特尔联合众厂商推出了针对数据中心,高性能计算,AI等领域的全新的Compute EXpress Link互联协议,并宣布与阿里巴巴、戴尔EMC、Facebook、谷歌、HPE、华为和微软联合共同成立CXL联盟,随后AMD和Arm也先后加入。CXL联盟在成立之初已发布了CXL 1.0版规范,随后又发布了改进的CXL 1.1版规范。

到了2020年年末,在PCIe 5.0规范的物理和电气接口上,CXL联盟宣布新的CXL 2.0规范。新规范增加了内存池的支持,以最大限度地提高内存利用率,并且提供了对持久性内存的标准化管理,允许与DDR同时运行,从而可以释放DDR用于其他用途,同时向后兼容CXL 1.1和CXL 1.0版规范。CXL作为一种开放性的互联协议,能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,满足现今高性能异构计算的要求,并且提供更高的带宽及更好的内存一致性。

CXL 2.0使得PCIe 5.0的应用进一步拓展,解决了CPU到设备、设备到设备之间的内存一致性和统一问题。

相比于消费级市场,数据吞吐量更高的数据中心和超级计算机是PCIe 5.0抢先占据的细分市场。目前边缘计算、机器学习、人工智能和5G网络等应用发展蓬勃,对带宽要求也高,相信一旦时机成熟,相关设备的推广应该会非常迅速,比如基于PCIe 5.0的企业级SSD就已经露面了。与消费级市场有所不同,在这个领域还有英伟达联合IBM开发的NVLink总线,在某些方面具有一定的竞争力,会对PCIe 5.0构成压力。

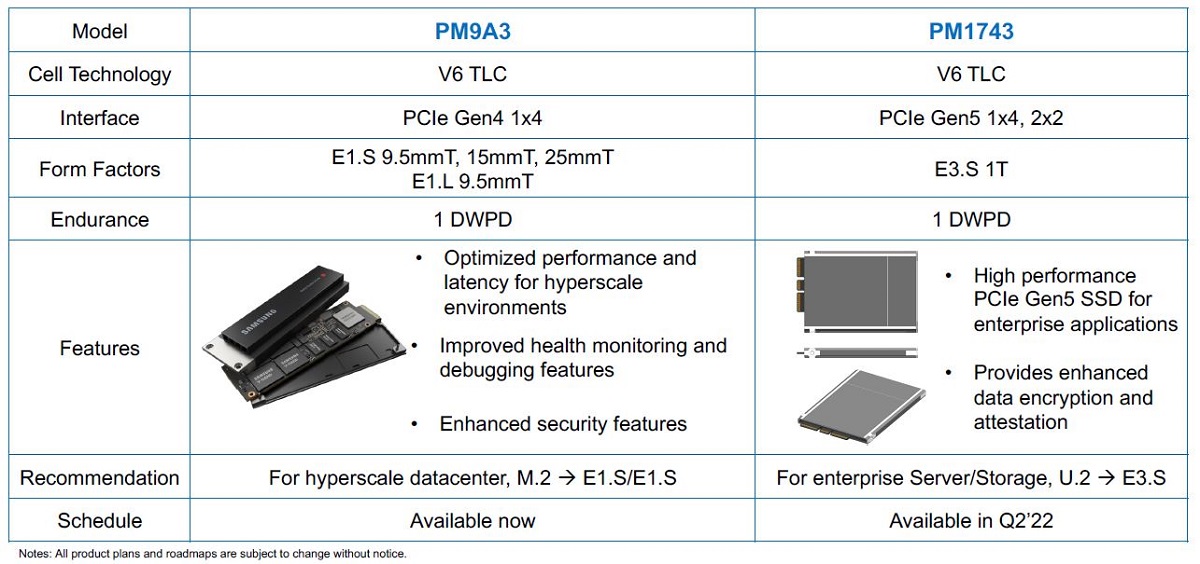

图:三星已公布基于PCIe 5.0的企业级SSD

反观消费级市场,虽然英特尔在Alder Lake平台已提供对PCIe 5.0的支持,但早期会欠缺一点动力。目前市场上有大量基于PCIe 3.0的设备,仍然处于向PCIe 4.0的过渡当中,对于带宽的需求也没那么迫切。不过下一代显卡有可能会支持PCIe 5.0,这应该是普通消费者最早接触到的PCIe 5.0设备。相信随着明年年末AMD发布Zen 4架构CPU,更换到AM5平台,提供对PCIe 5.0的支持后,相关设备会得到进一步普及,或许基于PCIe 5.0的消费级SSD也会出现。

目前PCIe标准规范制定工作已经到了第6代,也就是PCIe 6.0。

PCIe 6.0将把数据传输速率从PCIe 5.0的32 GT/s和PCIe 4.0的16 GT/s提高到每引脚64 GT/s,PCIe 6.0 ×16通道单向理论数据传输速度达到了128 GB/s(双向256 GB/s)。为了提高数据传输速率和带宽,新接口采用了四级脉冲振幅调制(PAM4)信令,这种信令也被用于像InfiniBand这种高端网络技术以及GDDR6X内存等地方。此外,PCIe 6.0还采用了低延迟前向纠错(FEC),以确保高效率运行。此外,未来新的CXL规范应该也会与PCIe 6.0相融合,提供更高效的解决方案。

如无意外,PCIe 6.0 1.0版本将会在今年年底或明年初公布,预计支持该平台产品将在2023年底或2024年的某个时候才上市。

ChinaBlue博士 2021-11-01 08:41 | 加入黑名单

感谢一下AMD,不是AMD我们现在连PCIe 4.0都见不到!

已有2次举报支持(38) | 反对(3) | 举报 | 回复

15#

VEGA教授 2021-10-30 10:42 | 加入黑名单

目前SSD标的那接近4.0极限的顺序读写速度实际上都是唬人的,生产力看缓外,家用娱乐看随机4K

已有2次举报顺序读写除了跑分外可以说根本没有应用场景了。

支持(23) | 反对(2) | 举报 | 回复

6#

VEGA教授 2021-10-31 23:34 | 加入黑名单

X570S芯片组带宽只有Z690一般,大把芯片组上挂三个4.0 M.2的。

芯片组的功能其实就和交换机一样,分配带宽很弹性,不存在同时满载的场景的。

已有2次举报X570S芯片组带宽只有Z690一般,大把芯片组上挂三个4.0 M.2的。

芯片组的功能其实就和交换机一样,分配带宽很弹性,不存在同时满载的场景的。

支持(7) | 反对(1) | 举报 | 回复

14#

cnbeta一代宗师 2021-10-31 19:08 | 加入黑名单

已有2次举报支持(2) | 反对(0) | 举报 | 回复

13#

VEGA教授 2021-10-31 11:15 | 加入黑名单

华硕除了最丐的Z690-P,从Z690-A开始都是四个M.2以上

已有2次举报华硕除了最丐的Z690-P,从Z690-A开始都是四个M.2以上

支持(4) | 反对(0) | 举报 | 回复

12#

VEGA教授 2021-10-31 11:14 | 加入黑名单

sata口ssd因为接口上限发展也停滞了,今年刚出的870EVO和几年前的860EVO性能完全一样。

因为现在用机械硬盘的人越来越少,再加上sata ssd发展停滞,所以现在主流平台已经不堆sata口了,现在一般主板只有4-6个sata,这个和芯片组带宽无关,是主板厂商设计时的取舍。

刚需多sata口只能选择HEDT或者WS级别的产品了。

已有2次举报sata口ssd因为接口上限发展也停滞了,今年刚出的870EVO和几年前的860EVO性能完全一样。

因为现在用机械硬盘的人越来越少,再加上sata ssd发展停滞,所以现在主流平台已经不堆sata口了,现在一般主板只有4-6个sata,这个和芯片组带宽无关,是主板厂商设计时的取舍。

刚需多sata口只能选择HEDT或者WS级别的产品了。

支持(5) | 反对(0) | 举报 | 回复

11#

cnbeta一代宗师 2021-10-30 18:53 | 加入黑名单

SATA随便一个辣鸡板都有4-6个。M.2接口部分多数只有一两个,甚至第二个还是不能满速的。带宽足够可以多加接口呀。

再者USB4要来了吧,不也得分带宽。

已有2次举报SATA随便一个辣鸡板都有4-6个。M.2接口部分多数只有一两个,甚至第二个还是不能满速的。带宽足够可以多加接口呀。

再者USB4要来了吧,不也得分带宽。

支持(5) | 反对(0) | 举报 | 回复

10#

zhaoyun980终极杀人王 2021-10-30 11:23 | 加入黑名单

PCIE4.0都还没用上,这就除了5.0,准备搞6.0了?

已有2次举报支持(18) | 反对(0) | 举报 | 回复

9#

VEGA教授 2021-10-30 10:51 | 加入黑名单

支持(4) | 反对(1) | 举报 | 回复

8#

VEGA教授 2021-10-30 10:47 | 加入黑名单

PCI-E 5.0 X16不要说目前了,不能拆分的话以后真的是一点卵用都没有。

5.0最大意义还是拆分,5.0 X8等效 4.0 X16 , 5.0 X4等效3.0 X16 如果可以灵活拆分的话那一个5.0 X16就会有很强的拓展性。

然而目前的问题是没有转接芯片把5.0转成4.0或者3.0的,也没有对应PCI-E 5.0的PLX芯片,所以撑到死还是8+8

而且Z690芯片组也只能拆分成8+8的5.0,不像以前的Z系芯片组可以拆分成8+4+4

目前intel上5.0是因为铜缆的极限就是5.0了,换句话说就是目前做5.0并不复杂,所以能加上就先加上了,至于有什么用处那现在当然是没有什么卵用了。

支持(11) | 反对(2) | 举报 | 回复

7#

QQ23870862终极杀人王 2021-10-30 00:05 | 加入黑名单

我PCIE4.0都没用过就换代了

已有1次举报支持(14) | 反对(0) | 举报 | 回复

5#

JaxonLau终极杀人王 2021-10-29 22:11 | 加入黑名单

坐等PCIE5.0的SSD

已有2次举报准备仍3.0跳到5.0

支持(6) | 反对(0) | 举报 | 回复

4#

终末之虚梦教授 2021-10-29 21:02 | 加入黑名单

已有1次举报支持(3) | 反对(1) | 举报 | 回复

3#

yjhercules终极杀人王 2021-10-29 19:51 | 加入黑名单

2#

cnbeta一代宗师 2021-10-29 19:44 | 加入黑名单

对带宽不怎么敏感的显卡,给5.0x16。

已有3次举报给带宽敏感的储存,4.0x4。

看不懂呀!

支持(11) | 反对(3) | 举报 | 回复

1#

提示:本页有 15 个评论因未通过审核而被隐藏