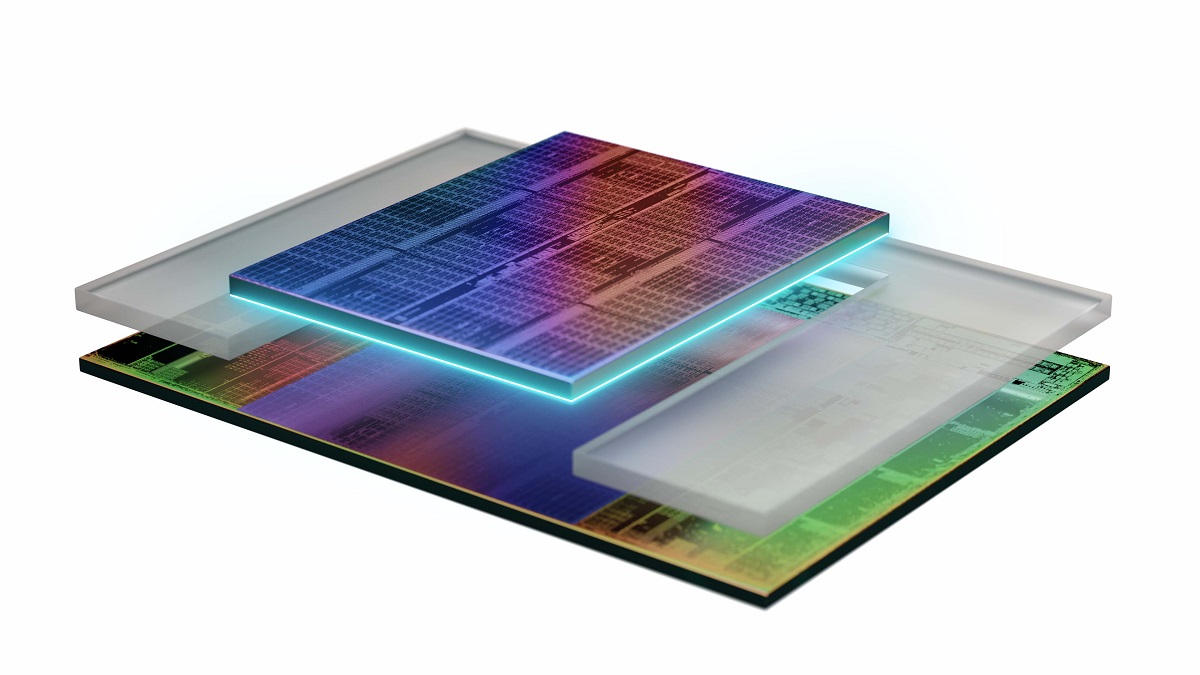

目前AMD采用3D垂直缓存(3D V-Cache)技术的Zen 4架构桌面处理器已经开始销售了,Ryzen 7000X3D系列处理器相比原有的普通型号,L3缓存容量均增加了64MB,成为了当今最好的游戏处理器。不过AMD并没有在Ryzen 7000X3D系列处理器材料中分享第二代3D V-Cache的细节,直到最近的ISSCC 2023里,才提供了一些具体的信息。

据TomsHardware报道,在第一代3D V-Cache里,AMD使用了7nm制造的SRAM芯片堆叠在同样7nm制造的Zen 3架构CCD上,而Zen 4架构CCD采用的是5nm工艺,会造成一些不匹配,为此AMD需要进行一些修改。

首先7nm的SRAM芯片变得更小,尺寸由41mm2缩小至36mm2,晶体管总数保持约47亿个,因此密度会更高。SRAM芯片也缺乏典型的缓存控制电路,这有助于减少延迟。额外的L3缓存会增加4个时钟的信号延迟,不过带宽已增加至2.5TB/s,相比之前第一代3D V-Cache的2TB/s提高了25%。

SRAM芯片通过两种类型的硅通孔(TSV)连接基础芯片,供电TSV在小芯片之间传输电力,而信号TSV在单元之间传输数据。在第一代3D V-Cache设计中,两种类型的硅通孔都在CCD的对应L3缓存区域内,不过由于Zen 4架构CCD采用的是5nm工艺,基础芯片的密度增加使得L3缓存区域变更小,即便新款SRAM芯片变得更小,也会与L2缓存出现重叠。

为此AMD将供电TSV移到了L2缓存区域,信号TSV仍在L3缓存区域。对于基础芯片,AMD在L3缓存、数据路径和控制逻辑上实现了0.68倍的有效面积缩放,通过对第一代3D V-Cache的优化改进,将L3缓存里的硅通孔区域缩小了50%,以减少新接口设计中的额外电路。

AMD的3D垂直缓存技术是基于台积电(TSMC)的SoIC技术,作为一种无损芯片堆叠技术,意味着不使用微凸点或焊料来连接两个芯片,硅通孔可以在没有任何类型的粘合材料的情况下进行匹配。第二代3D V-Cache在连接方面采用了基本相同的工艺,虽然做了改进,但最小TSV间距没有改变。此外,SRAM芯片与处理器内核保持在同一功率区域,无法独立调整,电压不能超过1.15V,所以小芯片的频率也不会太高。

AMD在ISSCC 2023上还展示了Ryzen 7000系列和EPYC处理器使用的6nm工艺IOD的大量细节,由于代号Genoa的EPYC处理器需要连接多达12个CCD,所以对应的IOD也十分地巨大。相比之下,消费级的Ryzen 7000系列处理器局限于两个CCD,这是一个不可改变的限制,因为对应的IOD只有两个GMI3互连接口连接CCD,所以最终限制了处理器的核心数量。

此前我们已经对Ryzen 9 7950X3D进行了评测,更大的L3缓存使其成为了当今最好的游戏处理器,想了解更详细内容可以点击《锐龙9 7950X3D天梯榜首发评测:大缓存就是给力,当前最佳游戏处理器》阅读。

zhaoyun980终极杀人王 2023-03-06 12:25 | 加入黑名单

第二代比第一代技术上并没有神恶魔大的改变嘛

已有2次举报支持(7) | 反对(0) | 举报 | 回复

1#

提示:本页有 1 个评论因未通过审核而被隐藏