欢迎参与评论,每一条合规评论都是对我们的褒奖。

请 登录 或 快速注册 后发表评论

CXL 2.0是一种让CPU与GPU、FPGA或其他加速器之间实现高速高效互联的规范,建立在PCIe 5.0标准的物理和电气接口上,与主DRAM一起使用的时候,可以扩大带宽和容量,能更好地满足人工智能(AI)等高性能计算的高速数据处理需求。

今年是人工智能应用全面爆发的一年,对高带宽的存储产品有了更为强烈的需求,不但大幅度拉升了DDR5及HBM类产品的出货量,也出现了更多支持CXL 1.1/2.0的产品,比如三星在今年5月推出了业界首款支持CXL 2.0的128GB CXL DRAM。国内厂商也不甘示弱,近日佰维就宣布推出CXL 2.0 DRAM。

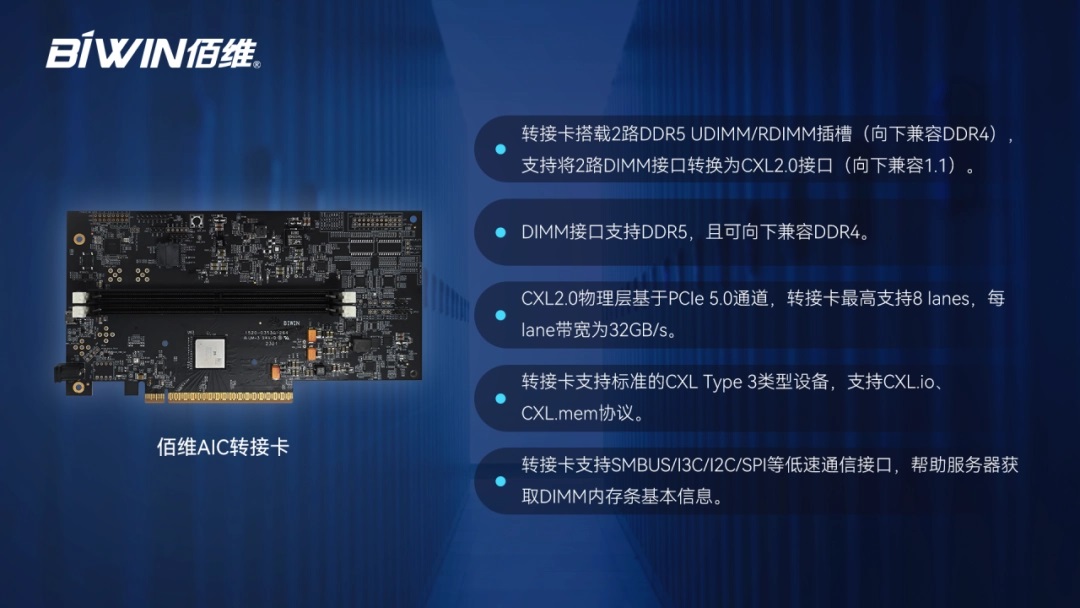

佰维的CXL 2.0 DRAM采用了EDSFF(E3.S)外形规格,尺寸为76(W)x 112.75(L)x 7.5(H)mm,支持PCIe 5.0 x8接口,带宽可达32 GB/s,支持Liunx Kernel 6.0及以上的系统,另外还支持On-Die ECC、Side-Band ECC、SDDC和SECDED等功能。佰维提供了32/64/96GB容量的DDR5产品,以不同容量规格满足不同用户对于计算应用的需求。此外,佰维还针对没有E3.S接口的服务器背板提供CXL AIC转接卡。

据了解,佰维已经向合作伙伴及客户提供了CXL 2.0 DRAM的样品,以进行测试和评估。随着越来越多的存储厂商推出支持CXL 2.0的产品,将加速下一代存储解决方案的商用化。