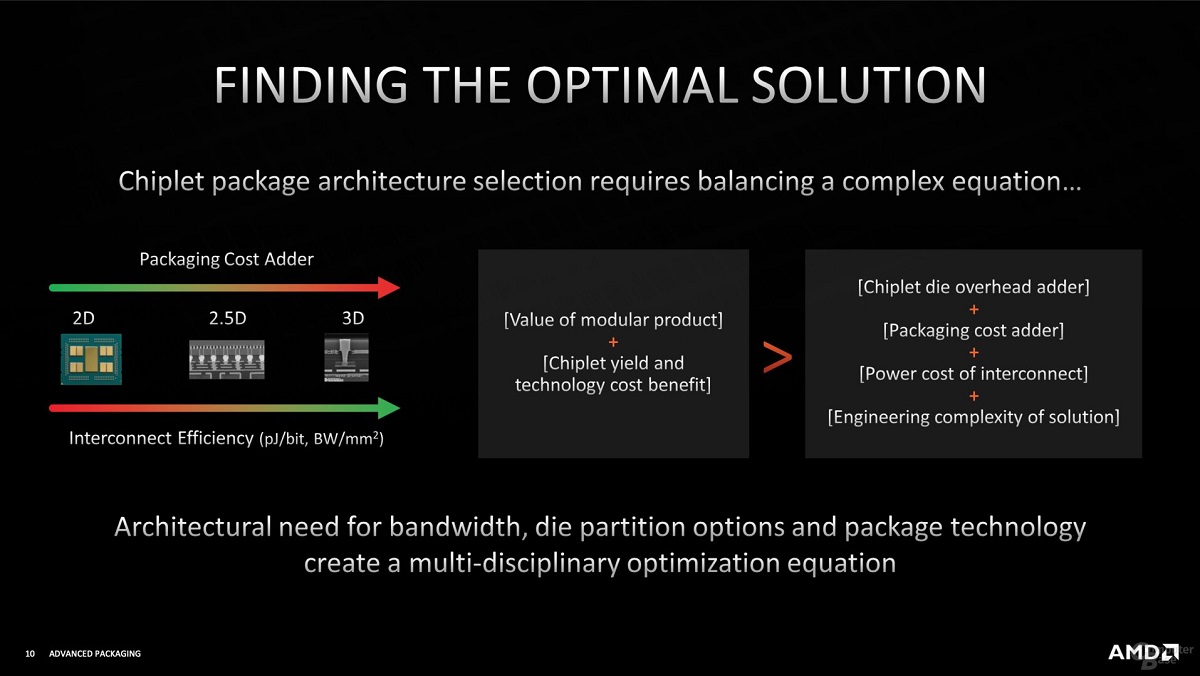

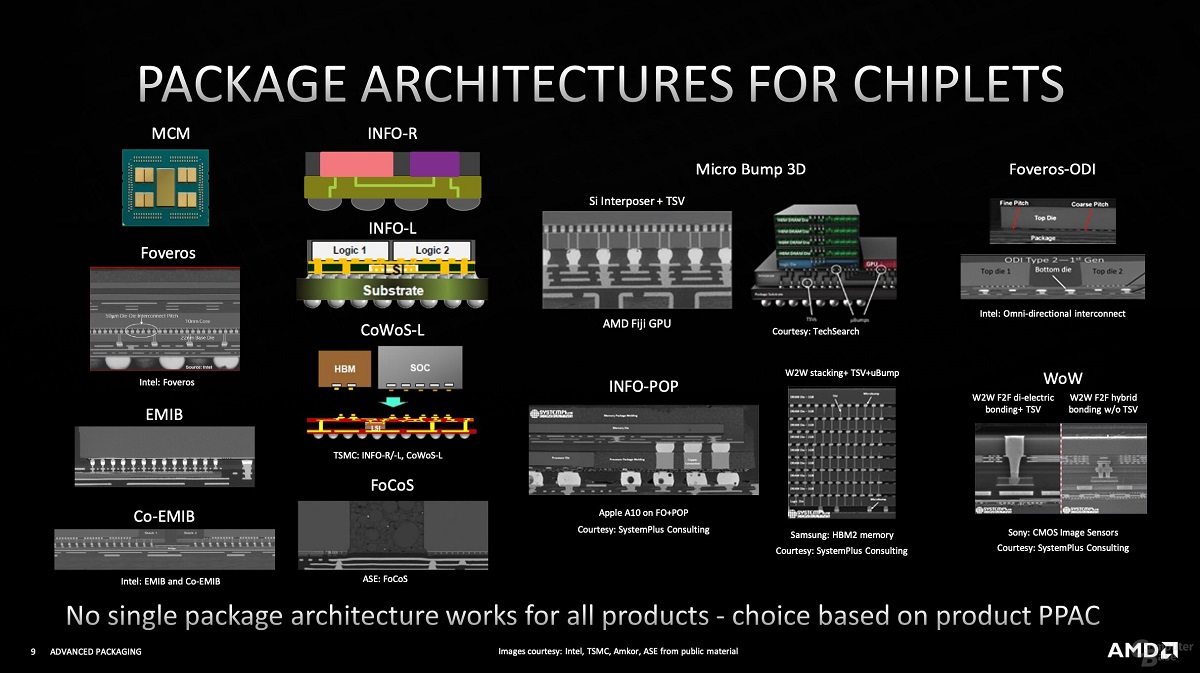

在Hot Chips 33上,AMD谈及了其3D堆栈技术的发展方向,还分享了3D V-Cache的一些细节。AMD表示,封装选择和芯片架构取决于具体产品的性能、功率、面积和成本,AMD称之为PPAC。如果将已经发布和即将推出的产品包括在内,AMD有14种多层小芯片设计的封装架构正在进行中。

据ComputerBase报道,AMD负责封装的高级研究员Raja Swaminathan表示,并非每个解决方案都适合所有产品,未来属于模块化设计和匹配协调的封装。这已经是业界的共识,各个厂商展示的解决方案都证明了这一点。不过所有厂商都关注经济效益,并非所有方案都适合消费市场,比如配备3D垂直缓存(3D V-Cache)技术的Zen 3架构桌面处理器,至少要有12核心的处理器才会用到。

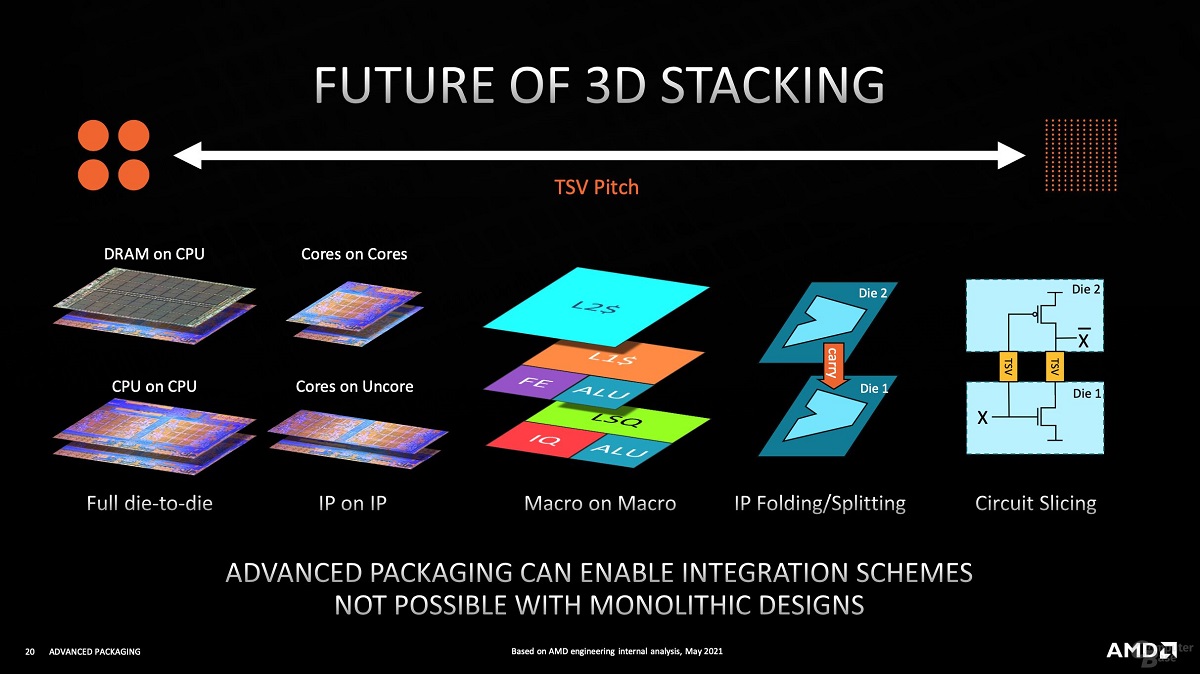

在六月份,AMD就介绍过其3D垂直缓存技术是基于台积电的SoIC技术。随着硅通孔(TSV)的增加,未来AMD会专注于更复杂的3D堆叠技术,比如核心堆叠核心,IP堆叠IP,甚至宏块可以3D堆叠。最终硅通孔的间距会变得非常紧密,以至于模块拆分、折叠甚至电路拆分都将成为可能,这会彻底改变今天对处理器的认知。

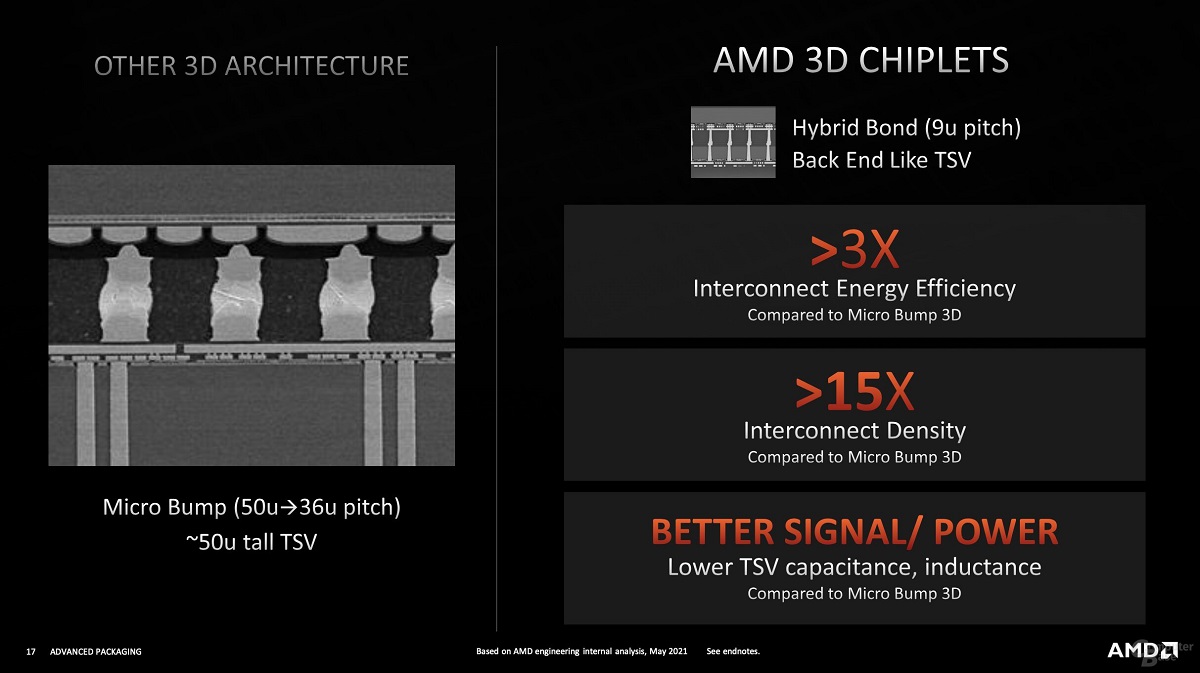

AMD分享了一些使用在Zen 3架构处理器上的3D V-Cache技术的信息,其中使用了3D微突(Micro Bump)和硅通孔互连方案,结合全新的亲水介电键合与Direct CU-CU键合技术。其混合键合的间距仅为9u,小于英特尔Forveros互连的10u间距 。 AMD预计其3D Chiplet技术提供3倍的互连能效,以及15倍的互连密度。

ssd444博士 2021-08-24 00:03 | 加入黑名单

支持(2) | 反对(0) | 举报 | 回复

10#

vigo93终极杀人王 2021-08-23 14:24 | 加入黑名单

支持(7) | 反对(0) | 举报 | 回复

9#

狐狸大仙研究生 2021-08-23 13:42 | 加入黑名单

已有1次举报支持(9) | 反对(0) | 举报 | 回复

8#

我匿名了 2021-08-23 13:21

已有1次举报支持(13) | 反对(1) | 举报 | 回复

7#

我匿名了 2021-08-23 13:17

支持(0) | 反对(0) | 举报 | 回复

6#

MIRAGES研究生 2021-08-23 13:06 | 加入黑名单

支持(5) | 反对(0) | 举报 | 回复

5#

vigo93终极杀人王 2021-08-23 12:22 | 加入黑名单

支持(7) | 反对(2) | 举报 | 回复

4#

cailiao1987教授 2021-08-23 11:54 | 加入黑名单

支持(16) | 反对(0) | 举报 | 回复

3#

传说中的的小白教授 2021-08-23 11:53 | 加入黑名单

"AMD表示,封装选择和芯片架构取决于具体产品的性能、功率、面积和成本,AMD称之为PPAC"——然而,用户担心的还是积热问题。

支持(2) | 反对(1) | 举报 | 回复

2#

Elwin终极杀人王 2021-08-23 11:30 | 加入黑名单

规模上去了,但是散热问题无法解决啊,像现在两家都出厂灰烬,我不信堆叠能解决散热?如果说每个核心2g多3g多是能解决,但是和现在的服务器cpu比又有什么区别呢,顶多成本下降了。

已有2次举报支持(1) | 反对(0) | 举报 | 回复

1#

提示:本页有 10 个评论因未通过审核而被隐藏