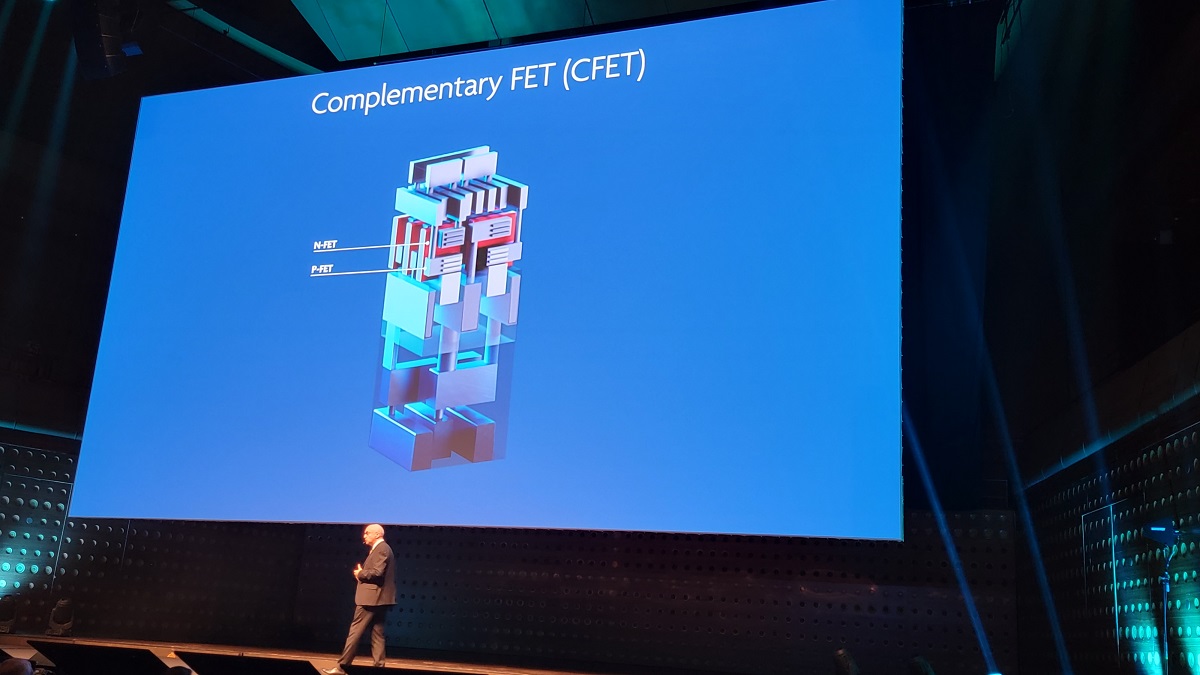

据eeNewEurope报道,英特尔和台积电(TSMC)即将在IEDM 2023上公布下一代CFET晶体管的进展情况。未来堆叠式CFET架构将取代GAA(Gate-All-Round),成为新一代晶体管设计。

CFET晶体管将n和p两种MOS器件相互堆叠在一起,需要使用高精度和高功率的High-NA EUV光刻机来制造。其概念最初由IMEC研究所于2018年提出,虽然早期探索研究主要集中在学术界,不过英特尔和台积电已经冒险进入该领域,积极展开下一代晶体管架构的研究。

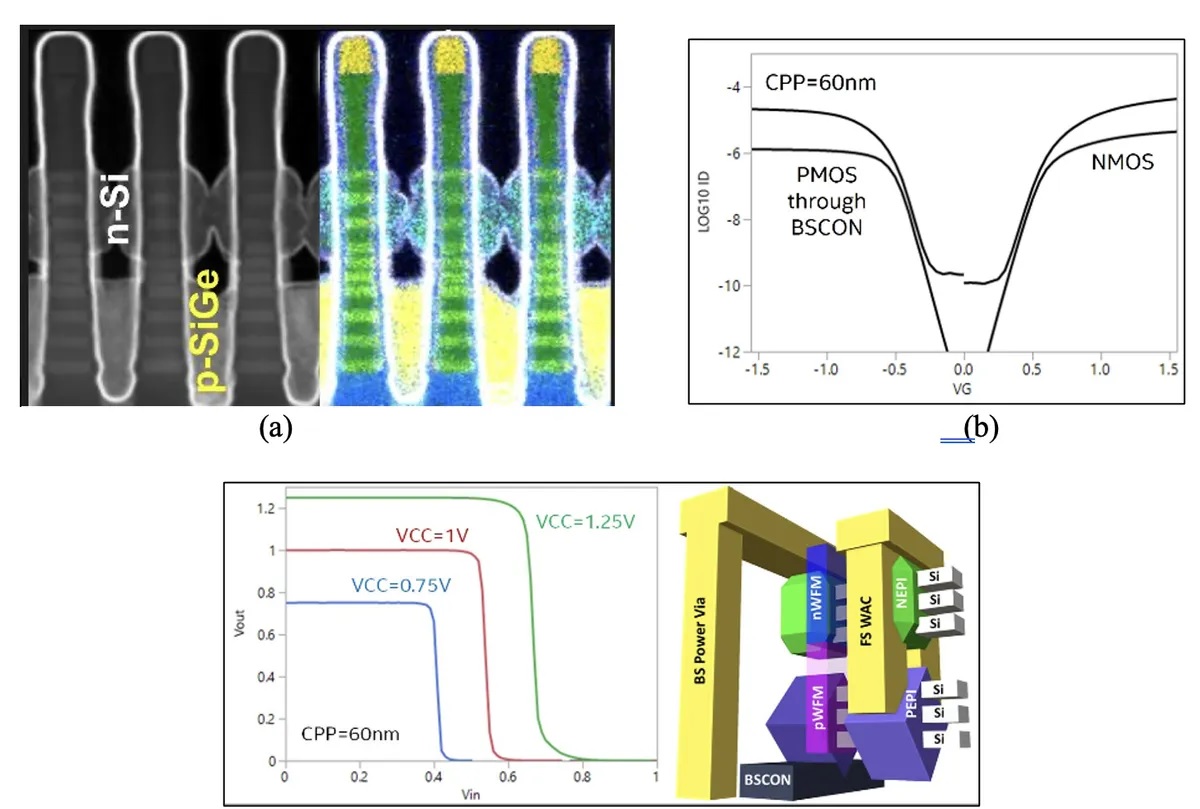

目前英特尔已建立了一个单片式3D CFET,将三条n-FET纳米片分布覆盖在三条p-FET纳米片之上,并保持30nm的垂直间隙。英特尔将报告取名为“采用电源通孔和直接背面组件触点60nm栅极间距的堆栈式CMOS逆变器演示”,描述了在60nm栅极间距上使用CFET的功能逆变器测试电路。该设计还采用垂直分层双电源漏外延和双金属闸极堆栈,并结合了英特尔的PowerVia背面供电技术。

台积电将讨论其实际操作CFET的方法,这是为制造逻辑芯片而量身定制的,具有48nm栅极间距。台积电的设计强调了层状n型纳米片晶体管置于p型晶体管之上,使其具有跨越六个数量级的开/关电流比。台积电已经证明了其设计的耐用性,90%以上的晶体管成功经受住了测试。不过台积电也承认,要充分利用CFET技术的能力,还有更多的功能需要吸收,目前正在进行的工作是实现这一目标的关键一步。

CFET技术为晶体管设计带来了明显的转变,其允许垂直堆栈两个晶体管安装在一个晶体管的面积内,可进一步提升芯片上晶体管的密度。这种设计不仅为提高空间使用提供解决方案,而且还促进了更精简的CMOS逻辑电路布局,有利于提高设计效率。CFET的既有结构可以减少寄生效应,从而为提高性能和功率效率创造了可能。此外,还能与背面供电等新技术相结合,可简化制程技术的复杂性。