欢迎参与评论,每一条合规评论都是对我们的褒奖。

请 登录 或 快速注册 后发表评论

三星在SEDEX 2022上,介绍了一种称为“BSPDN(背面供电网络)”的技术,称经过后端互联设计和逻辑优化,可以解决FSPDN(前端供电网络)造成的前端布线堵塞问题,2nm芯片的性能将提高44%,功率效率提高30%。在去年的VLSI研讨会上,三星又公布了最新的BSPDN研究成果,表示BSPDN相比FSPDN的面积可以减小14.8%。

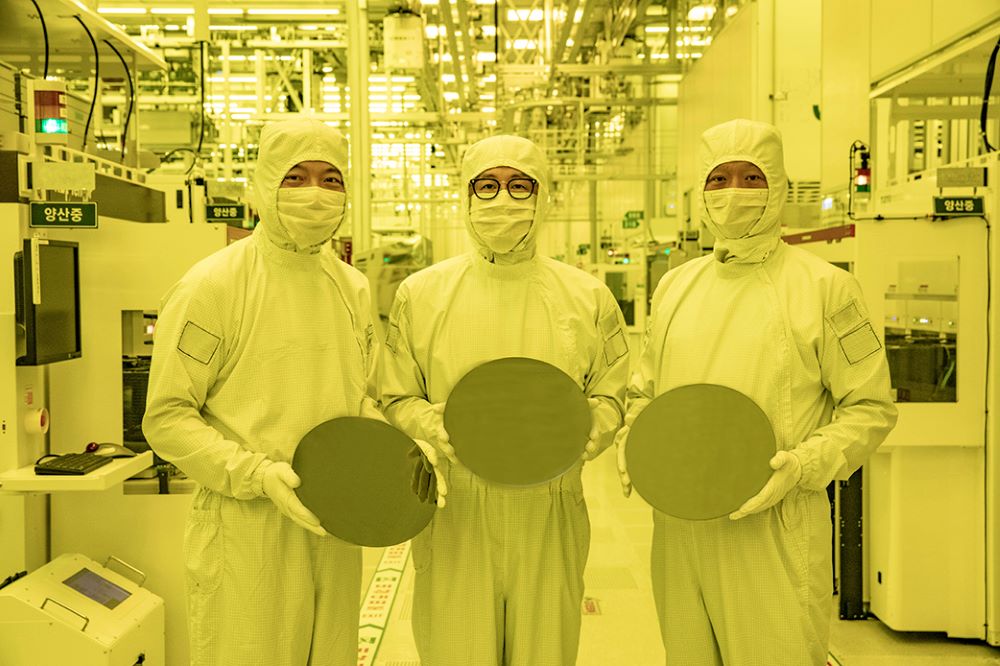

据相关媒体报道,三星正在推动BSPDN的应用,计划明年量产的2nm工艺引入背面供电技术。三星希望通过BSPDN改变游戏规则,让其能够更好地与台积电(TSMC)在代工业务上竞争。

传闻三星已经在两个Arm内核上进行了测试,设法更好地实践如何减少芯片的内核面积,应用BSPDN后,两个Arm内核的芯片面积分别减少了10%和19%。随着芯片面积的缩小,三星可以更有效地批量生产更小的SoC设计。早期的测试显示,引入背面供电技术还成功地提高了性能和能效,甚至超出了三星制定的指标。由于尚未商业化,只是初步的技术探索,暂时还不清楚对生产成本的影响。

除了三星以外,英特尔过去也介绍了开发中的PowerVia技术,计划在Intel 20A制程节点首次引入。这是英特尔独有的、业界首个背面供电网络,通过消除晶圆正面供电布线需求来优化信号传输。按照英特尔的说法,背面供电可以让晶体管供电的路径变得非常直接,可以减少信号串扰,降低功耗,同时解决了晶体管尺寸不断缩小带来的互连瓶颈。